前言

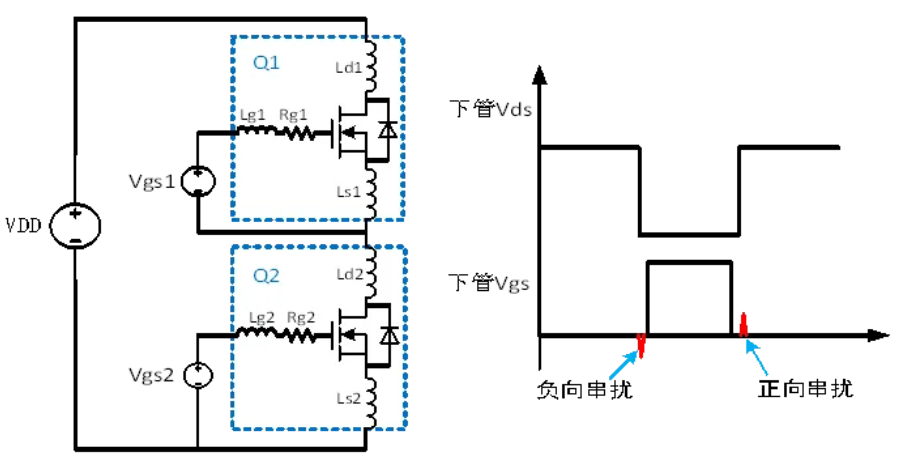

第三代宽禁带半导体材料SiC相对Si器件具有更快的开关速度,更高的耐压能力以及更好的温度特性,相应地带来更小的损耗,系统磁性元器件体积减小,功率密度的提升等优势。然而,随着SiC MOSFET开关频率的不断增加,在半桥结构(如逆变电路、全桥电路等)桥臂串扰现象越发严重,易造成桥臂直通短路或影响可靠性,限制了SiC MOSFET开关频率及系统功率密度进一步提高。

串扰产生原因

-

开关速度:SiC MOSFET具有更快的切换速度,在开关动作瞬间产生高 dv/dt(电压变化率)和高 di/dt(电流变化率)。

- 正 dv/dt:在米勒电容(Crss ,MOSFET 中漏极 - 栅极之间的电容)上产生流向驱动侧的位移电流,在栅极阻抗引起正向感应电压,叠加在栅源极上会引起栅源极电压抬升。

- 负 dv/dt :在米勒电容上产生流向器件侧的位移电流,在栅极阻抗引起负向感应电压,造成栅源极出现过大的电压负向峰值。

-

电路寄生参数:在半桥拓扑等电路结构中,线路存在寄生电感、寄生电容等,在开关动作时与器件相互作用产生串扰。

-

以半桥电路为例串扰过程分析 :

- 正向串扰:

当上管栅极电压达到阈值后沟道开启,电流换向,此时下管体 二极管承受反向电压,Vds2电压迅速上升,米勒效应产生位移电流在其门极产生压降。Lg为栅极引线杂感,位移电流Ig流过Lg2后,由楞次定律可知,产生左负右正的感应电动势VLg2,Vgs2=-V2+(VLg2+VRg2)式中-V2为SiC驱动负电压,VLg2为寄生电感感应电压,VRg2为内部Rg产生电压,因此在上管开通时,下管Vgs串扰电压为VLg2+VRg2,如该电压超过开通阈值电压Vth,将会导致上下直通的可能性。

图1 上下管开通及串扰过程

- 负向串扰:

当主上管栅极电压达到米勒电压,其漏源极电压开始上升,下漏源极电压Vds2开始下降,如图1所示。此时在下管门极产生的串扰电压和正向串扰公式一样,但电压电流变化率不同,该负向电压可能超过额定门极负压,对门极可靠性造成影响。

串扰影响

-

可能导致桥臂短路:如果正向串扰电压使另一原本应截止的开关管部分或完全导通,会导致上下桥臂同时导通,形成短路路径。

-

栅极损伤:负向串扰电压如果超过SiC MOSFET栅极负向额定电压,将造成栅极过应力,长期可能导致栅极损坏。

-

限制开关速度:在SiC MOSFET工作中产生串扰问题,可能限制原本SiC MOSFET可以达到更高开关速度。

抑制措施

-

降低开关速度:最为直观,但限制了其高频优势,使系统效率和功率密度有所折扣。

-

选择合适的负驱动电压:选择一个折中使正向串扰不高于阈值电压、负向串扰不超过额定负压的负驱动电压(不过较难选择,往往需要基于现有系统多次实验)。

-

增加辅助电路:在门极回路中添加辅助电路(如通过MOSFET、BJT等控制),给串扰提供一个低阻抗的路径,但增加了驱动设计难度和成本。

-

优化设计减小寄生参数:在设计时尽可能将寄生电感、电容等做到尽可能小。

-

技术改进

- 减小栅极引线阻抗:从而减小阻抗上的感应压降,抑制栅源极过压。

- 采用有源米勒箝位技术:泄放位移电流,有效保护SiC MOSFET器件。

- 通过三级关断串扰抑制技术:改善栅极驱动波形,有效抑制过大的电压正向抬升和负向电压。 -

器件选型:选择具有较低米勒电容(Crss)的碳化硅器件,能提高器件的抗干扰能力,降低器件在串扰行为下误导通的风险。